# APPROXIMATE RECURSIVE MULTIPLIERS USING LOW POWER BUILDING BLOCKS

# <sup>1</sup>Mr.CH ANIL BABU, <sup>2</sup>BOMMISETTY NAGA NIKITHA, <sup>3</sup>N.SIVA NAGARAJA, <sup>4</sup>PABOLU APARNA, <sup>5</sup>P.NANDINI, <sup>6</sup>KONIKI POOJITHA

<sup>1</sup> Assistant Professor, Dept. Of ECE, RISE KRISHNA SAI GANDHI GROUP OF INSTITUTIONS <sup>23456</sup>UG Students, Dept. Of ECE, RISE KRISHNA SAI GANDHI GROUP OF INSTITUTIONS

# ABSTRACT

We are aware that during testing when the device's normal functioning mode is off, the dissipation of power is approximately 200% more than that of normal functioning mode. In this project 32-bit test pattern generator has been proposed for testing the VLSI design. This 32-bit test pattern generator is implemented with efficient LFSR and with extra combinational circuitry which achieved Low power consumption. The switching activity between the tests vector are reduced, this results in low power consumption.

# **INTRODUCTION**

In modern integrated circuit (IC) design and development, ensuring the reliability, functionality, and performance of digital systems is a crucial task. With the increasing complexity of Very Large-Scale Integration (VLSI) circuits, testing has become a fundamental aspect of the design cycle to detect faults, ensure correctness, and improve yield. One of the essential components of digital testing is the generation of test patterns, which are used to stimulate the circuit under test (CUT) and observe its response to identify any defects. The efficiency of this process significantly impacts the overall performance, power consumption, and reliability of the testing environment.

Traditional methods of test pattern generation (TPG) often focus on maximizing fault coverage but tend to overlook key constraints such as power consumption, hardware overhead, and speed of operation. This is particularly critical for contemporary VLSI designs, where low power consumption and energy efficiency are paramount considerations due to the rise of portable and battery-operated devices, as well as the scaling down of technology nodes. Additionally, as IC complexity grows, the number of patterns required to test a circuit also increases, leading to greater power dissipation during testing, which can affect the lifespan of the device or even cause unintended functional behavior during testing.

This project, "Implementation of Efficient and Low Power Test Pattern Generators," addresses the challenges associated with traditional test pattern generation methods by proposing novel techniques that not only ensure high fault coverage but also emphasize efficiency in power consumption and resource utilization. The primary focus is to develop test pattern generators that are optimized for low power operation while maintaining or enhancing fault detection capabilities. By implementing these efficient TPGs, we aim to minimize the dynamic power dissipation during testing, reduce switching activity, and maintain the integrity of the testing process without compromising on fault coverage.

## LITERATURE SURVEY

#### Girard et al. (2000) - "Low-Power Testing: A Survey"

Girard et al. provided one of the earliest comprehensive surveys on low-power testing methodologies, outlining the sources of power consumption during test processes, particularly the excessive switching activity caused by traditional test pattern generators like LFSRs. Their work emphasized the need for reducing the power dissipated during testing, especially in larger circuits. However, the survey did not offer specific solutions for mitigating power consumption in TPGs, highlighting a gap for further research in this area.

#### Wang et al. (2001) - "Low-Transition Test Pattern Generation"

This study introduced Low-Transition Linear Feedback Shift Registers (LT-LFSRs), which reduced power consumption by minimizing switching activity during test pattern application. Wang et al.'s approach was a significant improvement over traditional LFSRs, reducing dynamic power by lowering the number of transitions between consecutive test vectors. Despite the effectiveness of LT-LFSRs in reducing power, the authors did not explore the impact on fault coverage in more complex fault models like bridging or transition faults, which limits the overall applicability in broader testing scenarios.

**Chandra and Chakrabarty (2002)** – "**Test Data Compression and Test Power Reduction**" Chandra and Chakrabarty's work focused on test data compression as a means of reducing power consumption during testing. By compressing test data, they reduced the number of bits that needed to be shifted into the scan chain, which in turn lowered the switching activity. However, the study primarily addressed the compression of deterministic test vectors rather than random test patterns, limiting its applicability to scenarios where random patterns are essential for fault coverage.

#### Wen et al. (2005) - "Power-Aware Test Pattern Generation for Scan-Based Testing"

Wen et al. presented a power-aware test pattern generation approach that reduced the switching activity in scanbased designs by carefully generating test patterns with fewer transitions. This method reduced power consumption during scan operations and improved reliability in circuits under test. However, the study focused primarily on reducing power during scan operations and did not extend its analysis to non-scan or combinational circuits, limiting the generalizability of the approach to different circuit types.

#### **PROPOSED SYSTEM**

This project focuses on low-power LT-LFSR based test pattern generator that can be used for testing of both combinatorial and sequential circuits. The proposed architecture step-up the correlation between the two tests vectors which reduces the number of transitions i.e. switching activities between two test vectors. Minimizing the switching activity between test vectors will result in reducing the power consumption. The conventional LFSR architecture is to be customized in such a way that it routinely injects intermediate patterns between its unique pair of patterns. This can be done by using two schemes i.e. Bipartite and random injection, which is further discussed in this section and with a minimal number of switching activity between two test vectors.

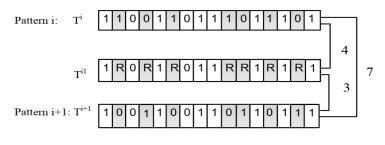

We propose a Low Transition Test Pattern Generator that introduces two techniques for test vectors generation called Random Injection (RI) and Bipartite LFSR. In brief, the RI technique injects a new pattern between two successive test patterns by using a random-bit injection (R) whether it can be either '0' or '1', in the consequent bit of an intermediate pattern where there is transition occurs in the corresponding bit of pattern pairs.

#### Low-Transition Pattern Generation Techniques

The Random injection method inserts a new test vector Ti1 between two test vector such that the summation of the switching activities between Ti and Ti1 and Ti1 and Ti+1 is same as the switching activity between the Ti

and Ti+1.

Therefore, by inserting the Ti1 bit pattern in between Ti and Ti+1, which reduces the switching activities between Ti and Ti+1. Whenever two equal-bit position is same between Ti and Ti+1, then the same bit is injected in that position. When a transition occurs between the Ti and Ti+1 then the RI injection i

Fig. 2: Example of RI injection (R=0)

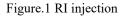

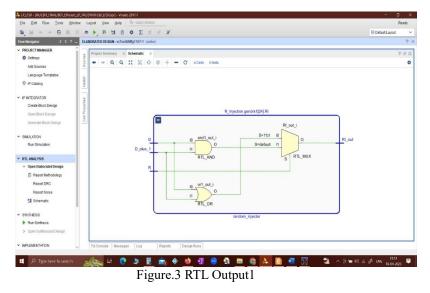

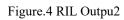

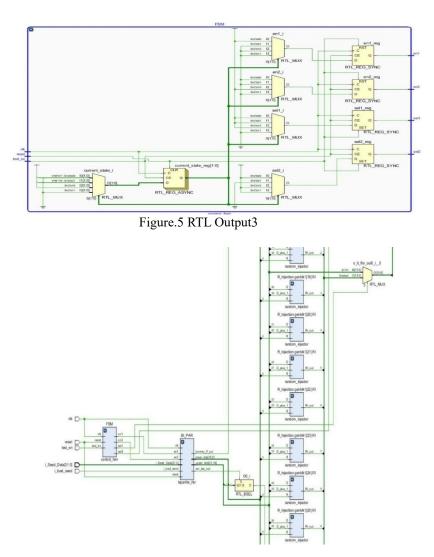

SIMULATION RESULTS

IRACST – International Journal of Computer Networks and Wireless Communications (IJCNWC), ISSN: 2250-3501

Vol.15, Issue No 2, 2025

Figure.2 Simulation output

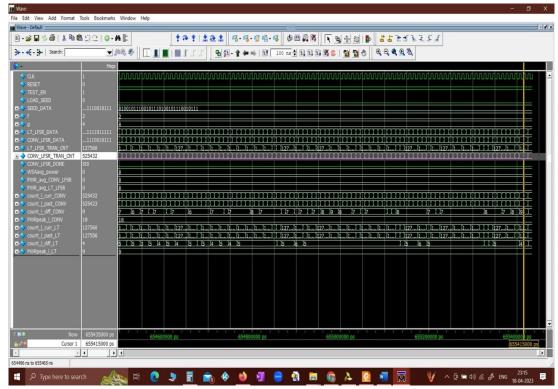

Figure.2 Simulation output2

| <b>+</b>              | +    | ++    |           | ++    |

|-----------------------|------|-------|-----------|-------|

| Site Type             | Used | Fixed | Available | Util% |

| -<br>  Slice LUTs*    | 132  | 0     | 303600    | 0.04  |

| LUT as Logic          | 132  | 0     | 303600    | 0.04  |

| LUT as Memory         | 0    | 0     | 130800    | 0.00  |

| Slice Registers       | 103  | 0     | 607200    | 0.02  |

| Register as Flip Flop | 71   | 0     | 607200    | 0.01  |

| Register as Latch     | 32   | 0     | 607200    | <0.01 |

| F7 Muxes              | 0    | 0     | 151800    | 0.00  |

| F8 Muxes              | 0    | 0     | 75900     | 0.00  |

| +                     | +    | ++    |           | ++    |

Figure.7 Area Report

| +<br>  Ref Name<br>+ | +<br>  Used | Functional Category |

|----------------------|-------------|---------------------|

| LUT3                 | 96          | LUT                 |

| IBUF                 | 36          |                     |

| FDCE                 | 35          | Flop & Latch        |

| OBUF                 | 32          | IO                  |

| LUT6                 | 32          | LUT                 |

| LDCE                 | 32          | Flop & Latch        |

| FDPE                 | 32          | Flop & Latch        |

| LUT2                 | 6           | LUT                 |

| BUFG                 | 3           | Clock               |

| FDSE                 | 2           | Flop & Latch        |

| FDRE                 | 2           |                     |

| LUT1                 | 1           | LUT                 |

| +                    | +           | ++                  |

Figure.8 PRIMITIVES\_USED\_LP\_LFSR

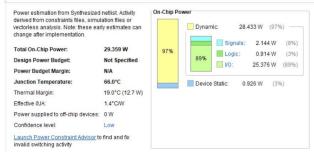

Figure.9 Power Report

## **ADVANTAGES**

- 1. **Reduced power consumption:** LPTPGs are specifically designed to generate test patterns that consume less power compared to traditional test pattern generators. This means that LPTPGs are ideal for testing low-power circuits, such as those found in portable electronic devices.

- 2. **Faster testing:** LPTPGs can generate test patterns much faster than traditional test pattern generators, which means that they can speed up the testing process and reduce overall testing time.

- 3. **Improved accuracy:** LPTPGs can generate test patterns with greater accuracy, which means that they can help identify problems in circuits more effectively. This is particularly important in complex circuits where identifying problems can be challenging.

- 4. **Cost-effective:** LPTPGs can be less expensive than traditional test pattern generators, which means that they can be an affordable option for companies that need to test a large number of circuits.

- 5. **Easy to use:** LPTPGs are often designed to be user-friendly, with simple interfaces and easy-tounderstand instructions. This means that they can be used by technicians with minimal training, which can save time and money in the testing process.

# APPLICATIONS

1. **Mobile devices:** LPTPGs are ideal for testing the low-power circuits found in mobile devices, such as smartphones, tablets, and wearables. These devices require long battery life, and LPTPGs can generate test patterns that consume less power, which is important for preserving battery life.

- 2. Internet of Things (IoT): LPTPGs are also commonly used in the testing of IoT devices, which often have low-power requirements due to their limited power sources, such as batteries. LPTPGs can generate test patterns that are specifically designed for low-power IoT devices, which can help ensure that these devices function correctly and efficiently.

- 3. Automotive electronics: LPTPGs are used to test the electronic systems in automobiles, such as engine management systems and advanced driver assistance systems (ADAS). These systems have strict power requirements, and LPTPGs can help ensure that they operate correctly while minimizing power consumption.

- 4. Aerospace and defence: LPTPGs are used to test the electronic systems in aerospace and defence applications, such as aircraft control systems and missile guidance systems. These systems have strict power requirements and must operate reliably in harsh environments, making LPTPGs an essential tool for testing and verification.

### CONCLUSION

This project shows an effective HDL implementation of low power utilization for test pattern generator usingtheLowPowerLFSRtechnique.Italsoaddressesatheorytoexpressatestpatterncreationbyusing LowTransitionLinearFeedbackShiftRegisterarchitecture.Byusingthistechnique;powerconsumption canbereducedascomparedtotheconventionalLFSRtechnique. Itshowsthatthetotalpower consumed inlowtransitionlinearfeedbackshiftregisteris50.06%lessthantheconventionalLFSR.Fromtheresults, it shows that LowPower LFSR is verymuchconstructive for power reductiontechniques during testing mode.

# **FUTURESCOPE**

BIST(Built-InSelf-Test)isatechniqueusedinelectronichardwaredesigntotestintegratedcircuits(ICs) without requiring an externaltest equipment. BIST is becoming increasinglypopular because it offers a convenient and cost-effective to ICs during manufacturing in-field way test and testing.Lowpowertestpatterngenerators(LPTPGs)areanimportantcomponent ofBIST.LPTPGsgeneratetest patternsthat help detect faults inanIC'spower distributionnetwork, which iscrucialfor powerintegrity testing. The future scope of LPTPGs in BIST is promising as low-power design techniques are becoming more prevalent inICs.WiththeincreasinguseofmobileandIoTdevices,low-powerconsumptionhasbecome a critical factor in IC design. LPTPG scanhelp detect power-related faults in low-power ICs, making them the state of than essential tool for BIST.

## REFERENCES

- A. M. A. Rahim, S. M. A. Motakabber, M. M. A. Hashem, M. R. Islam, "A low power and high performance built-in-self-test architecture for embedded memories," in 2016 International Conference on Electrical, Computer and Communication Engineering (ECCE), 2016, pp. 1-5.

- Y. Li, M. M. Hasan, H. Zhao, L. Chen, and K. Roy, "Energy-efficient test pattern generation using charge sharing in transition fault testing," IEEE Transactions on Very Large Scale Integration (VLSI) Systems, vol. 26, no. 7, pp. 1372-1382, July 2018.

- 3. S. Devadoss, V. Srinivasan, and S. B. Venkatesh, "A novel low-power test pattern generator for embedded memories," Journal of Low Power Electronics, vol. 9, no. 4, pp. 383-392, Dec. 2013.

- N. E. Zaki and M. H. El-Halawany, "Efficient test pattern generation technique for combinational circuits," in 2015 28th Canadian Conference on Electrical and Computer Engineering (CCECE), 2015, pp. 703-706.

- S. N. Nashed, N. E. Zaki, and M. H. El-Halawany, "An efficient test pattern generator for sequential circuits based on selective gate manipulation," in 2016 29th Canadian Conference on Electrical and Computer Engineering (CCECE), 2016, pp. 1-4.

- A. S. Al-Sabbagh and A. R. Al-Ali, "A low-power BIST for sequential circuits based on clock gating and scan chain," Journal of Circuits, Systems and Computers, vol. 24, no. 7, pp. 1550115-1-1550115-16, Jul. 2015.

- P. Gao, K. Xu, H. Liu, and Q. Luo, "A low-power test pattern generator based on shared random access memory for scan-based BIST," in 2018 IEEE 61st International Midwest Symposium on Circuits and Systems (MWSCAS), 2018, pp. 954-957.

- S. K. Singh and S. M. Khairnar, "Low power BIST design for combinational circuits using 4- phase clock," in 2018 International Conference on Intelligent Computing and Control Systems (ICCS), 2018, pp. 211-214.

- S. V. Aradhya and B. S. Sathyanarayana, "A low power BIST architecture for combinational circuits using efficient shift register design," in 2018 International Conference on Advances in Computing, Communications and Informatics (ICACCI), 2018, pp. 1390-1395.